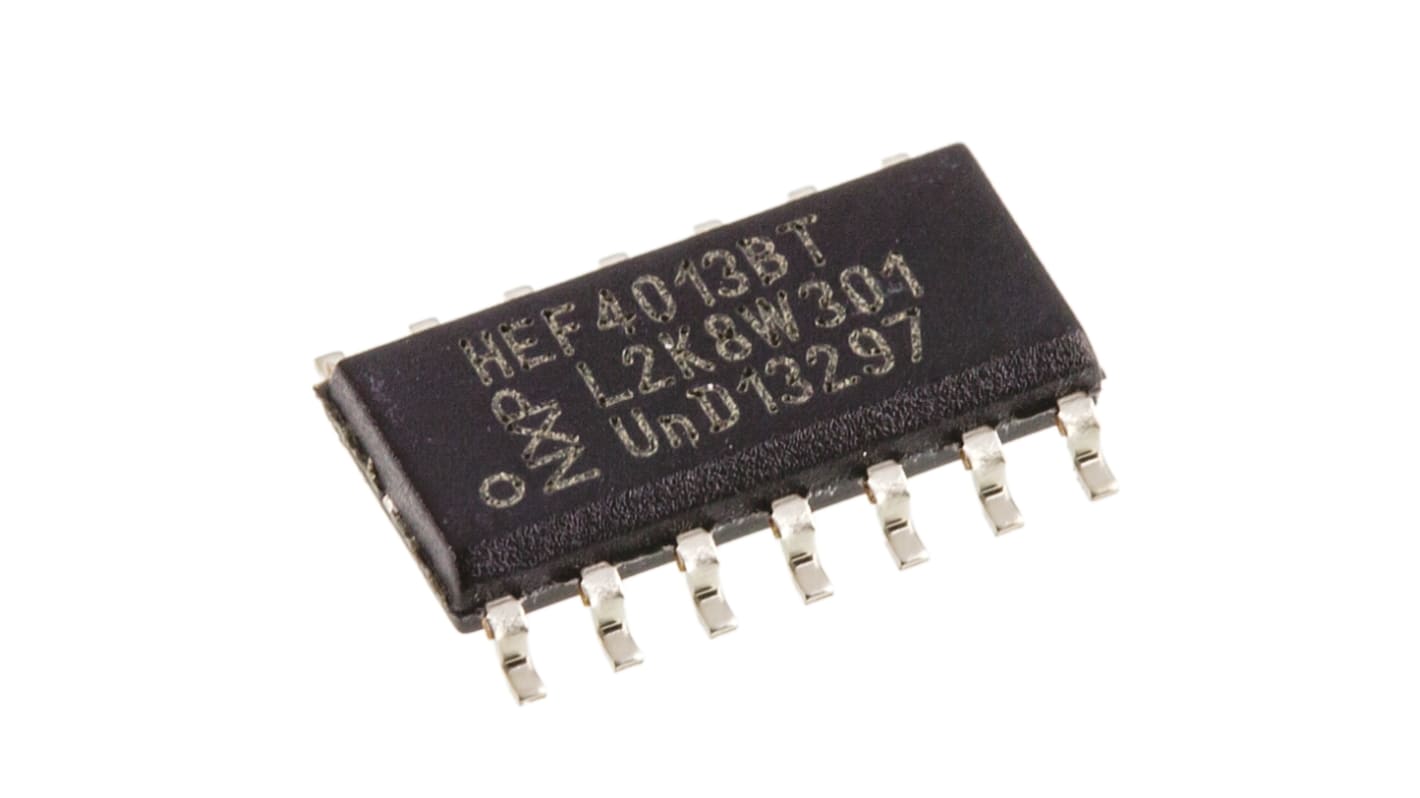

IC flip flop HEF4013BT,652, Dual, SOIC, 14-Pin

- Codice RS:

- 103-8389

- Codice costruttore:

- HEF4013BT,652

- Costruttore:

- Nexperia

Alternativa

Prodotto al momento non disponibile. Ti suggeriamo la seguente alternativa.

Unità (Su Bobina da 2500)

0,12 €

(IVA esclusa)

0,15 €

(IVA inclusa)

- Codice RS:

- 103-8389

- Codice costruttore:

- HEF4013BT,652

- Costruttore:

- Nexperia

Seleziona tutto | Attributo | Valore |

|---|---|---|

| Marchio | Nexperia | |

| Famiglia logica | 4000 | |

| Funzione logica | Tipo D | |

| Tipo di ingresso | Single Ended | |

| Tipo di segnale in uscita | Differenziale | |

| Tipo di trigger | Fronte positivo | |

| Polarità | Invertente, non invertente | |

| Tipo di montaggio | Montaggio superficiale | |

| Tipo di package | SOIC | |

| Numero pin | 14 | |

| Set/Reset | Si | |

| Numero di elementi per chip | 2 | |

| Ritardo di propagazione massimo @ CL max | 220 ns @ 5 V | |

| Tensione di alimentazione operativa massima | 15 V | |

| Dimensioni | 8.75 x 4 x 1.45mm | |

| Larghezza | 4mm | |

| Massima temperatura operativa | +125 °C | |

| Condizioni di test ritardo di propagazione | 50pF | |

| Lunghezza | 8.75mm | |

| Altezza | 1.45mm | |

| Minima temperatura operativa | -40 °C | |

| Tensione di alimentazione operativa minima | 3 V | |

| Seleziona tutto | ||

|---|---|---|

Marchio Nexperia | ||

Famiglia logica 4000 | ||

Funzione logica Tipo D | ||

Tipo di ingresso Single Ended | ||

Tipo di segnale in uscita Differenziale | ||

Tipo di trigger Fronte positivo | ||

Polarità Invertente, non invertente | ||

Tipo di montaggio Montaggio superficiale | ||

Tipo di package SOIC | ||

Numero pin 14 | ||

Set/Reset Si | ||

Numero di elementi per chip 2 | ||

Ritardo di propagazione massimo @ CL max 220 ns @ 5 V | ||

Tensione di alimentazione operativa massima 15 V | ||

Dimensioni 8.75 x 4 x 1.45mm | ||

Larghezza 4mm | ||

Massima temperatura operativa +125 °C | ||

Condizioni di test ritardo di propagazione 50pF | ||

Lunghezza 8.75mm | ||

Altezza 1.45mm | ||

Minima temperatura operativa -40 °C | ||

Tensione di alimentazione operativa minima 3 V | ||

Link consigliati

- IC flip flop HEF4013BT Dual Buffer 14-Pin

- IC flip flop 74HC73D Dual SOIC, 14-Pin

- IC flip flop 74HC74D Dual SOIC, 14-Pin

- IC flip flop HEF4027BT Dual 16-Pin

- IC flip flop 74HC123D Dual SOIC, 16-Pin

- IC flip flop 74HCT112D Dual LSTTL 16-Pin

- IC flip flop MC14013BDG SOIC, 14-Pin

- IC flip flop HCF4013YM013TR SOIC, 14-Pin