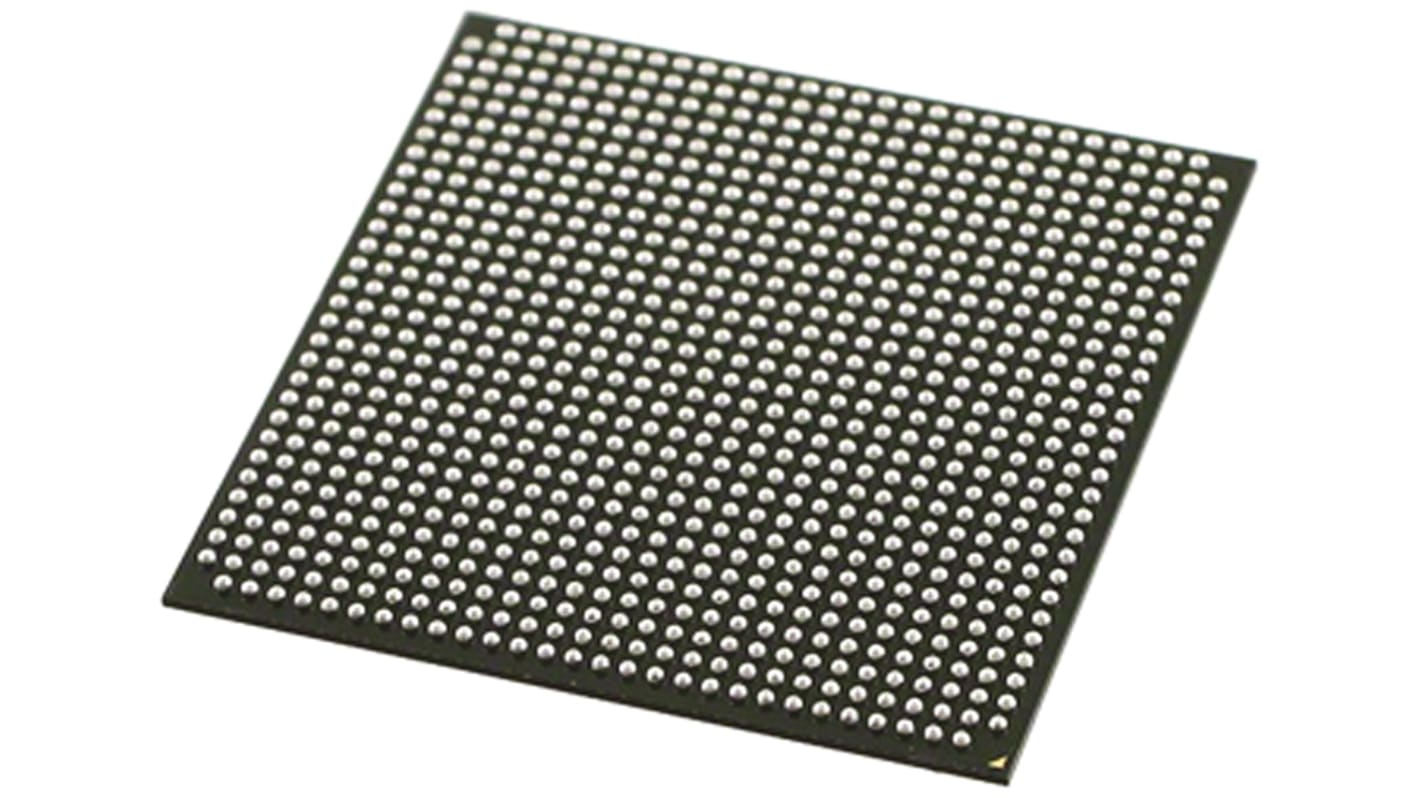

FPGA Altera 5CSEMA6F31C8N Cyclone V SE, 110000 celle, 110000 gate, RAM 5761K, 41509 block, FBGA 896 Pin, 1,8 →

- Codice RS:

- 830-3574

- Codice costruttore:

- 5CSEMA6F31C8N

- Costruttore:

- Altera

Al momento non disponibile

Non sappiamo se questo articolo tornerà in stock, RS intende rimuoverlo a breve dall'assortimento.

- Codice RS:

- 830-3574

- Codice costruttore:

- 5CSEMA6F31C8N

- Costruttore:

- Altera

Specifiche

Documentazione Tecnica

Normative

Dettagli prodotto

Trova prodotti simili selezionando uno o più attributi.

Seleziona tutto | Attributo | Valore |

|---|---|---|

| Marchio | Altera | |

| Famiglia | Cyclone V SE | |

| Numero di gate logici | 110000 | |

| Numero di celle logiche | 110000 | |

| Numero di unità logiche | 41509 | |

| DSP dedicato | Sì | |

| Numero di registri | 166036 | |

| Numero di moltiplicatori | 224 (18 x 18) | |

| Tipo di montaggio | Montaggio superficiale | |

| Tipo di package | FBGA | |

| Numero pin | 896 | |

| Numero di bit RAM | 5761K | |

| Lunghezza | 31mm | |

| Tensione di alimentazione operativa massima | 3,3 V | |

| Tensione di alimentazione operativa minima | 1,8 V | |

| Larghezza | 31mm | |

| Massima temperatura operativa | +85 °C | |

| Minima temperatura operativa | 0 °C | |

| Seleziona tutto | ||

|---|---|---|

Marchio Altera | ||

Famiglia Cyclone V SE | ||

Numero di gate logici 110000 | ||

Numero di celle logiche 110000 | ||

Numero di unità logiche 41509 | ||

DSP dedicato Sì | ||

Numero di registri 166036 | ||

Numero di moltiplicatori 224 (18 x 18) | ||

Tipo di montaggio Montaggio superficiale | ||

Tipo di package FBGA | ||

Numero pin 896 | ||

Numero di bit RAM 5761K | ||

Lunghezza 31mm | ||

Tensione di alimentazione operativa massima 3,3 V | ||

Tensione di alimentazione operativa minima 1,8 V | ||

Larghezza 31mm | ||

Massima temperatura operativa +85 °C | ||

Minima temperatura operativa 0 °C | ||

Cyclone FPGA, Altera

Un FPGA è un dispositivo a semiconduttore costituito da una matrice di blocchi logici configurabili (CLB) collegati tramite interconnessioni programmabili. L'utente stabilisce le interconnessioni attraverso la programmazione SRAM. Un CLB può essere semplice (porte AND, OR, ecc.) o complesso (un blocco di RAM). L'FPGA consente di effettuare modifiche a un progetto anche una volta che il dispositivo è stato saldato in un circuito stampato.