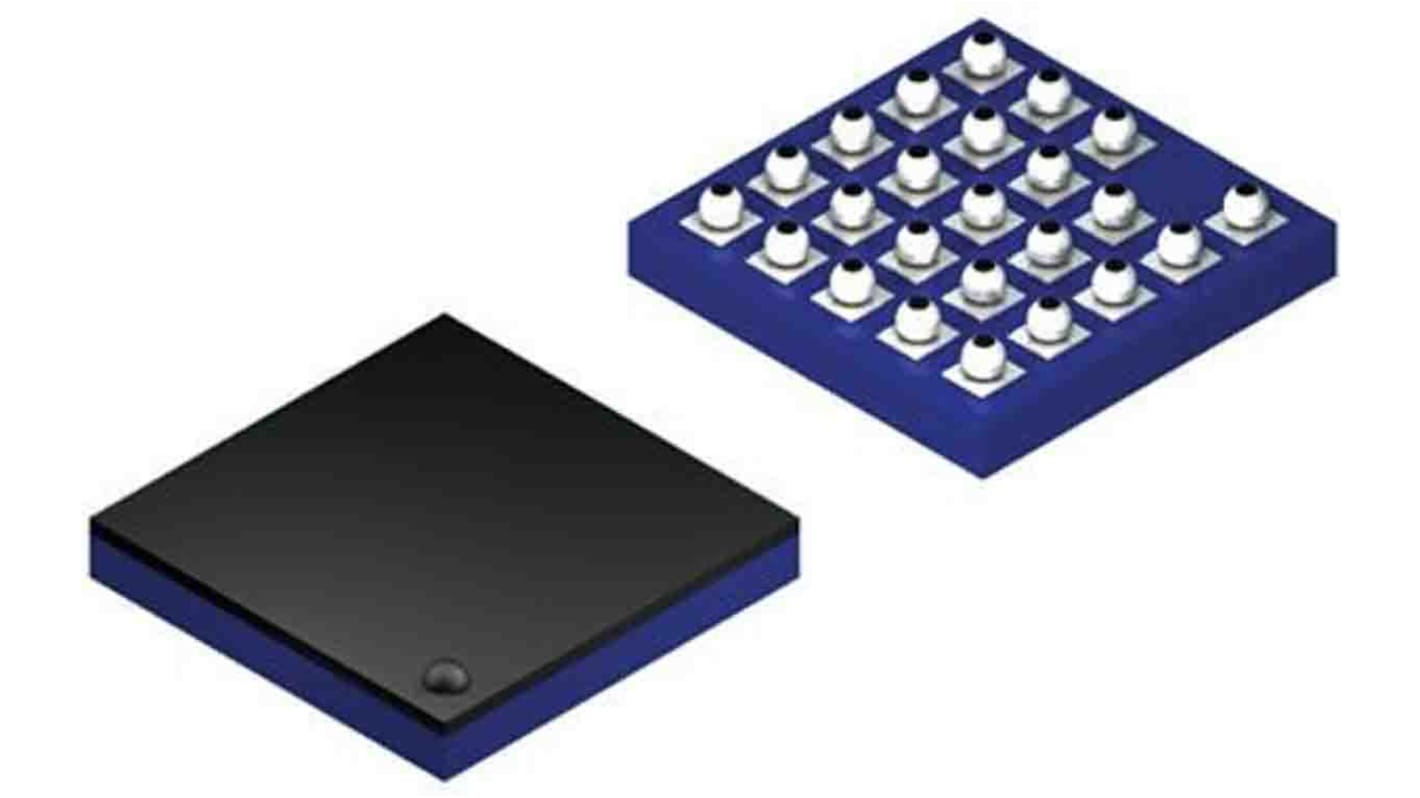

Memoria Flash Infineon NOR, 512 MB, BGA, 24 Pin, CFI, SPI S25FL512SAGBHID10

- Codice RS:

- 193-8764

- Codice costruttore:

- S25FL512SAGBHID10

- Costruttore:

- Infineon

Sconto per quantità disponibile

Prezzo per 1 confezione da 2 unità*

9,31 €

(IVA esclusa)

11,358 €

(IVA inclusa)

Consegna GRATUITA per ordini a partire da 60,00 €

Temporaneamente esaurito

- Spedizione a partire dal 10 agosto 2026

Te ne servono di più? Inserisci la nuova quantità e clicca su "Controlla le date di consegna".

Unità | Per unità | Per confezione* |

|---|---|---|

| 2 - 8 | 4,655 € | 9,31 € |

| 10 - 18 | 4,53 € | 9,06 € |

| 20 - 98 | 4,415 € | 8,83 € |

| 100 - 198 | 4,30 € | 8,60 € |

| 200 + | 4,195 € | 8,39 € |

*prezzo indicativo

- Codice RS:

- 193-8764

- Codice costruttore:

- S25FL512SAGBHID10

- Costruttore:

- Infineon

Specifiche

Documentazione Tecnica

Normative

Dettagli prodotto

Trova prodotti simili selezionando uno o più attributi.

Seleziona tutto | Attributo | Valore |

|---|---|---|

| Marchio | Infineon | |

| Tipo prodotto | Memoria Flash | |

| Dimensione memoria | 512MB | |

| Tipo di interfaccia | CFI, SPI | |

| Tipo di package | BGA | |

| Numero pin | 24 | |

| Frequenza di clock massima | 133MHz | |

| Tipo montaggio | Superficie | |

| Tipo di cella | NOR | |

| Tensione minima di alimentazione | 1.65V | |

| Tensione massima di alimentazione | 3.6V | |

| Tipo di temporizzazione | Sincrono | |

| Minima temperatura operativa | -40°C | |

| Temperatura massima di funzionamento | 85°C | |

| Lunghezza | 8mm | |

| Standard/Approvazioni | No | |

| Altezza | 0.95mm | |

| Numero parole | 64M | |

| Numero bit per parola | 8 | |

| Tempo massimo di accesso casuale | 14.5ns | |

| Numero banchi | 4 | |

| Serie | S25FL512S | |

| Standard automobilistico | AEC-Q100 | |

| Seleziona tutto | ||

|---|---|---|

Marchio Infineon | ||

Tipo prodotto Memoria Flash | ||

Dimensione memoria 512MB | ||

Tipo di interfaccia CFI, SPI | ||

Tipo di package BGA | ||

Numero pin 24 | ||

Frequenza di clock massima 133MHz | ||

Tipo montaggio Superficie | ||

Tipo di cella NOR | ||

Tensione minima di alimentazione 1.65V | ||

Tensione massima di alimentazione 3.6V | ||

Tipo di temporizzazione Sincrono | ||

Minima temperatura operativa -40°C | ||

Temperatura massima di funzionamento 85°C | ||

Lunghezza 8mm | ||

Standard/Approvazioni No | ||

Altezza 0.95mm | ||

Numero parole 64M | ||

Numero bit per parola 8 | ||

Tempo massimo di accesso casuale 14.5ns | ||

Numero banchi 4 | ||

Serie S25FL512S | ||

Standard automobilistico AEC-Q100 | ||

Questo dispositivo si collega a un sistema host tramite un'interfaccia Periferica seriale (SPI). L'ingresso e l'uscita seriali SPI a singolo bit (SingleI/o o SIO) tradizionali sono supportati, nonché i comandi seriali opzionali a due bit (Dual i/o o DIO) e a quattro bit (Quad i/o QIO). Questa interfaccia multiplwidth è chiamata SPI Multi-i/o o MIO. Inoltre, la famiglia FL-S aggiunge il supporto per i comandi di lettura Double Data Rate (DDR) per SIO, DIO e QIO che trasferiscono l'indirizzo e leggono i dati su entrambi i fronti del clock.L'architettura Eclipse dispone di un Page Programming buffer che consente di programmare fino a 256 parole (512 byte) in un'unica operazione, con conseguente faster efficace programmazione e cancellazione rispetto al programma SPI di generazione precedente o algoritmi di cancellazione. L'esecuzione del codice direttamente dalla memoria flash è spesso chiamata Execute-In-Place o XIP. Utilizzando dispositivi FL-S alle velocità di clock più elevate supportate, con i comandi QIO o DDR-QIO, la velocità di trasferimento di lettura delle istruzioni può corrispondere o superare le tradizionali interfacce parallele, asincrone, NÉ memorie flash, riducendo drasticamente il numero di segnali.il prodotto S25FL512S offre densità elevate, unite alla flessibilità e alle prestazioni veloci richieste da una varietà di applicazioni embedded. È ideale per lo shadowing del codice, XIP e l'archiviazione dei dati.

Link consigliati

- Memoria Flash Infineon NOR BGA CFI, SPI

- Memoria Flash Infineon NOR BGA CFI, SPI S25FL512SAGBHI310

- Memoria Flash Infineon NOR BGA SPI

- Memoria Flash Infineon NOR BGA SPI S26HL512TFPBHI000

- Memoria Flash Infineon NOR BGA SPI S25HS512TFABHI010

- Memoria Flash Infineon NOR BGA SPI S25HS512TDPBHI010

- Memoria Flash Infineon NOR BGA SPI S25HL512TFABHI010

- Memoria Flash Infineon NOR BGA SPI S26HL512TFPBHI010