- Codice RS:

- 188-2580

- Codice costruttore:

- W9712G6KB25I

- Costruttore:

- Winbond

Prodotto al momento non disponibile. La consegna avverrà entro 4 giorni lavorativi a partire dal 02/12/2024.

Aggiunto

Prezzo per Unità

1,664 €

(IVA esclusa)

2,03 €

(IVA inclusa)

| Unità | Per unità | Per Vassoio* |

| 209 + | 1,664 € | 347,776 € |

| *prezzo indicativo | ||

- Codice RS:

- 188-2580

- Codice costruttore:

- W9712G6KB25I

- Costruttore:

- Winbond

Documentazione Tecnica

Normative

Dettagli prodotto

W9712G6KB è una SDRAM DDR2 a 128M bit e la velocità coinvolge -25, 25I e -3.

Architettura della velocità di trasferimento dati doppia: due trasferimenti dati per ciclo di clock

Latenza CAS: 3, 4, 5 e 6

Lunghezza del treno d'impulsi: 4 e 8

Valori di dati strobo differenziali bidirezionali (DQS e /DQS ) sono strasmessi / ricevuti con i dati

Allineamento Edge con dati di lettura e allineamento centrale con dati di scrittura

DLL allinea le transizioni DQ e DQS con clock

Ingressi di clock differenziali (CLK e /CLK)

Maschere di dati (DM) per la scrittura di dati

I comandi immessi su ogni bordo CLK positivo, i dati e la maschera dati sono referenziati a entrambi i bordi di /DQS

Posted /CAS programmable additive latency supported to make command and data bus efficiency

Latenza di lettura = Latenza Aggiuntiva più Latenza CAS (RL = al + CL)

Regolazione dell'impedenza Off-Chip-Driver (OCD) e On-Die-Termination (ODT) per una migliore qualità del segnale

Funzionamento automatico di precarica per treni d'impulsi di lettura e scrittura

Aggiornamento automatico e modalità di aggiornamento automatico

Spegnimento precaricato e spegnimento attivo

Scrivi Maschera Dati

Latenza di scrittura = Latenza di lettura - 1 (WL = RL - 1)

Interfaccia: SSTL_18

Latenza CAS: 3, 4, 5 e 6

Lunghezza del treno d'impulsi: 4 e 8

Valori di dati strobo differenziali bidirezionali (DQS e /DQS ) sono strasmessi / ricevuti con i dati

Allineamento Edge con dati di lettura e allineamento centrale con dati di scrittura

DLL allinea le transizioni DQ e DQS con clock

Ingressi di clock differenziali (CLK e /CLK)

Maschere di dati (DM) per la scrittura di dati

I comandi immessi su ogni bordo CLK positivo, i dati e la maschera dati sono referenziati a entrambi i bordi di /DQS

Posted /CAS programmable additive latency supported to make command and data bus efficiency

Latenza di lettura = Latenza Aggiuntiva più Latenza CAS (RL = al + CL)

Regolazione dell'impedenza Off-Chip-Driver (OCD) e On-Die-Termination (ODT) per una migliore qualità del segnale

Funzionamento automatico di precarica per treni d'impulsi di lettura e scrittura

Aggiornamento automatico e modalità di aggiornamento automatico

Spegnimento precaricato e spegnimento attivo

Scrivi Maschera Dati

Latenza di scrittura = Latenza di lettura - 1 (WL = RL - 1)

Interfaccia: SSTL_18

Specifiche

Attributo | Valore |

|---|---|

| Dimensioni memoria | 128Mbit |

| Organizzazione | 16M x 8 bit |

| Classe SDRAM | DDR2 |

| Flusso dati | 200MHz |

| Larghezza del bus dati | 16bit |

| Larghezza del bus indirizzi | 15bit |

| Numero di bit per parola | 8bit |

| Tempo di accesso casuale massimo | 0.4ns |

| Numero di parole | 16M |

| Tipo di montaggio | Montaggio superficiale |

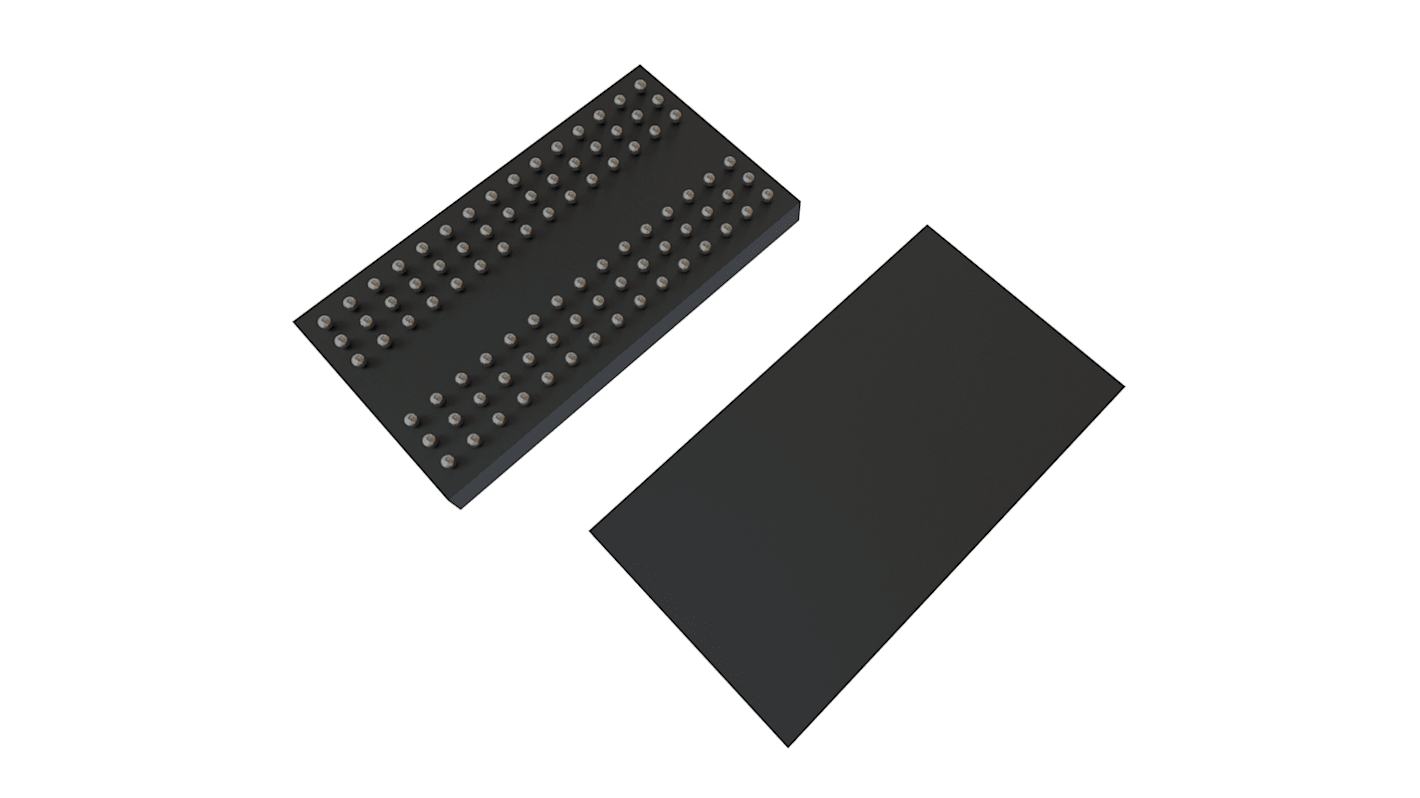

| Tipo di package | TFBGA |

| Numero pin | 84 |

| Dimensioni | 12.6 x 8.1 x 0.8mm |

| Altezza | 0.8mm |

| Lunghezza | 12.6mm |

| Massima temperatura operativa | +95 °C |

| Minima temperatura operativa | -40 °C |

| Larghezza | 8.1mm |

| Tensione di alimentazione operativa massima | 1,9 V |

| Tensione di alimentazione operativa minima | 1,7 V |

Link consigliati

- SDRAM AS4C128M16D2A-25BCN 400MHz7 V a 1 FBGA 84 Pin DDR2

- SDRAM W971GG6NB25I 800MHz7 V a 1,9 V 84 Pin DDR2

- SDRAM W971GG8NB25I 800MHz7 V a 1 VFBGA 60 Pin DDR2

- SDRAM W972GG6KB25I 800MHz7 V a 1 WBGA 84 Pin DDR2

- SDRAM W949D2DBJX5I 200MHz7 V a 1 VFBGA 90 Pin LPDDR

- SDRAM W949D6DBHX5I 200MHz7 V a 1 VFBGA 60 Pin LPDDR

- SDRAM AS4C64M16D2A-25BIN 400MHz7 V a 1 FBGA 84 Pin DDR2

- SDRAM W9751G6NB25I 400MHz7 V a 1 VFBGA 84 Pin DDR2