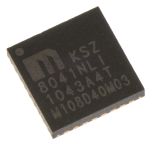

PHY

Il chip di interfaccia Ethernet PHY è un componente transceiver per la trasmissione e la ricezione di dati o frame Ethernet.

Ethernet è una specifica di interfaccia stabilita in IEEE 802.3. Uno degli elementi di IEEE 802.3 è il livello fisico Ethernet o PHY.

Il livello fisico specifica i tipi di segnali elettrici, velocità di segnalazione, tipi di supporti e connettori, topologie di rete.

Cos'è PHY Ethernet

Il PHY costituisce l'interfaccia fisica responsabile della codifica e decodifica dei dati tra un sistema puramente digitale e il mezzo su cui i segnali vengono trasmessi.

Rappresenta quindi un ponte tra i livelli di connessione digitale ed elettrica dell'interfaccia.

I chip PHY possono essere componenti discreti o possono anche essere integrati nei controller Ethernet.

Come funziona PHY Ethernet

Ethernet PHY è un ricetrasmettitore che funge da ponte tra il mondo digitale e il mondo analogico. Inclusi processori, array di gate programmabili sul campo (FPGA) e circuiti integrati specifici per l'applicazione (ASIC).

L'Ethernet PHY è connesso a un media access controller (MAC) che solitamente è integrato in un processore, FPGA o ASIC, e controlla la parte del livello di collegamento dati del modello OSI.

L'interfaccia indipendente dai media (MII) definisce l'interfaccia tra il MAC e il PHY.

Velocità

Un'interfaccia PHY Ethernet è progettata per fornire una trasmissione priva di errori su una varietà di supporti in modo da raggiungere distanze superiori a 100 m.

Esistono molte varianti diverse dello standard Ethernet, con PHY corrispondenti, che vanno da 1 Mbps a 100 Gbps.

La maggior parte delle applicazioni Ethernet utilizza un PHY da 10/100 Mbps o 10/100/1000 Mbps.

I supporti fisici che trasportano i dati al PHY Ethernet includono doppini intrecciati, CAT5, cavi coassiali, backplane e fibre ottiche.